? 10nm、7nm��、5nm……隨著芯片制程節(jié)點越來越先進���,研發(fā)生產(chǎn)成本持續(xù)走高�����,而良率日益下降��,物理瓶頸正拖累摩爾定律的腳步�����。

? 像搭樂高積木一樣的小芯片(Chiplet)正成為AMD�、英特爾�����、臺積電����、Marvell、Cadence等芯片巨頭為摩爾定律續(xù)命的共同選擇之一����。

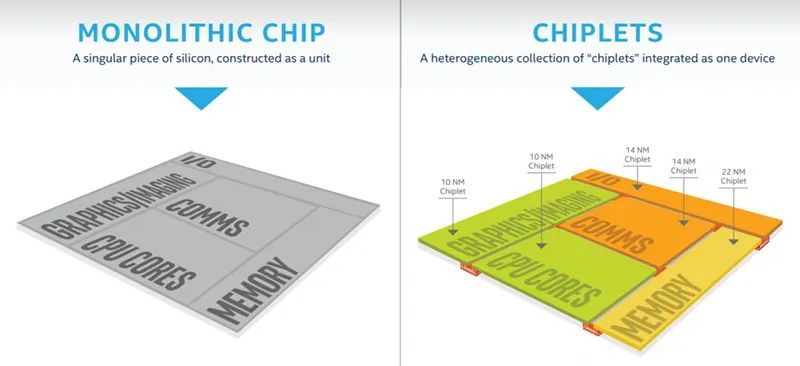

? 以前芯片由多個IP核心集成后統(tǒng)一封裝成單片芯片,而小芯片方法可將來自不同公司設(shè)計和封裝的小芯片組合在一起��,從而構(gòu)建更為高效和經(jīng)濟的芯片系統(tǒng)。

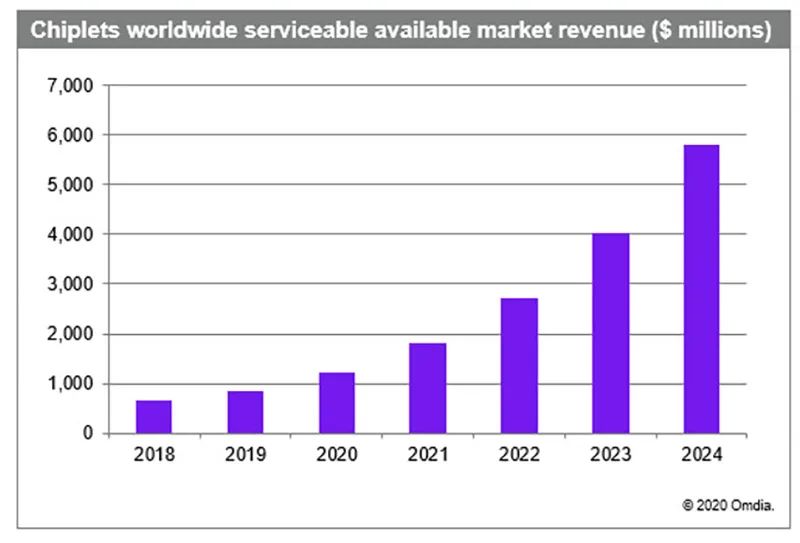

? 這種新型設(shè)計方法不僅能大大簡化芯片設(shè)計復(fù)雜度�,還能有效降低設(shè)計和生產(chǎn)成本。? 知名市場研究機構(gòu)Omdia預(yù)測,小芯片將在2024年全球市場規(guī)模擴大到58億美元���,較2018年的6.45億美元增長9倍。而長遠來看���,2035年小芯片市場規(guī)模有望增至570億美元�。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?▲2018-2024年全球小芯片市場收入

? 圍繞小芯片的新戰(zhàn)事,正在將芯片性能進化引向更具經(jīng)濟效益的未來���。

01

續(xù)命摩爾定律!小芯片時代來了

? 55年前�����,被推崇為芯片界“圣經(jīng)”的摩爾定律預(yù)言:當(dāng)價格不變時,集成電路上可容納的晶體管數(shù)量每隔18-24個月會增加一倍�����,性能也隨之提升一倍。

? 當(dāng)年摩爾定律的出現(xiàn)設(shè)定了極為關(guān)鍵的技術(shù)發(fā)展節(jié)奏基準�����,催化了科技市場欣欣向榮�����,為整個IT行業(yè)帶來了難以估量的經(jīng)濟價值�����。? 使用先進節(jié)點的好處很多,晶體管密度更大�、占用空間更少、性能更高�����、功率更低,但挑戰(zhàn)也越來越難以克服�。? 極小尺寸下,芯片物理瓶頸越來越難以克服��。尤其在近幾年,先進節(jié)點走向10nm����、7nm、5nm�,問題就不再只是物理障礙了�,節(jié)點越進化�����,微縮成本越高,能扛住經(jīng)濟負擔(dān)的設(shè)計公司越來越少�����。? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?▲隨著制程節(jié)點進化,芯片成本快速增長? 根據(jù)公開報道�,28nm節(jié)點設(shè)計成本約為5000萬美元�,而到5nm節(jié)點����,設(shè)計總成本已經(jīng)飆高到逾5億美元�,相當(dāng)于逾35億人民幣�����。

? 而守住摩爾定律,關(guān)乎利潤最大化����,如果研發(fā)和生產(chǎn)成本降不下來�,那么對于芯片巨頭和初創(chuàng)公司來說都將是糟糕的經(jīng)濟負擔(dān)。? 幸運的是�����,每當(dāng)摩爾定律被唱衰將走到盡頭���,總會激發(fā)出科學(xué)家和工程師們創(chuàng)新構(gòu)想����,提出力挽狂瀾的突破性技術(shù)��,將看似走向終結(jié)的摩爾定律一再推向遠方。? 基于小芯片的模塊化設(shè)計�,正是其中解決成本問題的一個極為關(guān)鍵的構(gòu)想�。

02

小芯片的三大價值:開發(fā)快���、成本低、功能多

? 當(dāng)前芯片設(shè)計模式常從不同IP供應(yīng)商購買軟核IP或硬核IP��,再結(jié)合自研模塊集合成一個片上系統(tǒng)(SoC),然后以某個制造工藝節(jié)點生產(chǎn)出芯片�。

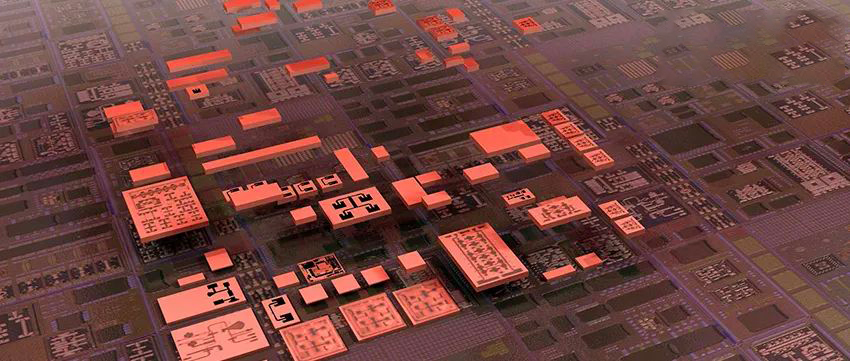

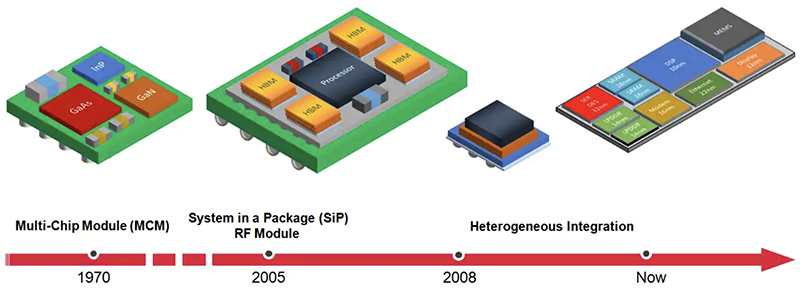

? 而小芯片通過先進封裝技術(shù)�����,能將多種不同架構(gòu)��、不同工藝節(jié)點、甚至來自不同代工廠的專用硅塊或IP塊集成在一起����,可以跳過流片,快速定制出一個能滿足多種功能需求的超級芯片產(chǎn)品�����。▲由中介層上多個小芯片組成的小芯片系統(tǒng)(來源:Cadence)? 相比單片芯片��,小芯片帶來的好處是多重的����。

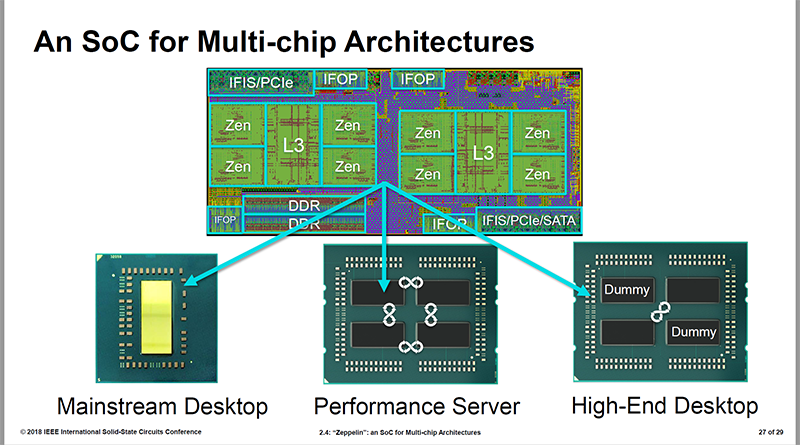

? 在服務(wù)器等計算系統(tǒng)中���,電源和性能由CPU核心和緩存支配���。通過將內(nèi)存與I/O接口組合到一個單片I/O芯片上�,可減少內(nèi)存與I/O間的瓶頸延遲,進而幫助提高性能�����。? 因為小芯片是由不同的芯片模塊組合而成���,設(shè)計者可在特定設(shè)計部分選用最先進的技術(shù),在其他部分選用更成熟���、廉價的技術(shù)��,從而節(jié)省整體成本��。? 例如,AMD第二代EPYC服務(wù)器處理器Ryzen采用小芯片設(shè)計,將更先進的臺積電7nm工藝制造的CPU模塊與更成熟的格羅方德12/14nm工藝制造的I/O模塊組合��,7nm可滿足高算力的需求,12/14nm則降低了制造成本�。? 這帶來的好處是,7nm制程部分的芯片面積大幅縮減�,而采用更成熟制程的I/O模塊有助于整體良率的提升��,進一步降低晶圓代工成本。綜合來看���,CPU核心越多����,小芯片組合的成本優(yōu)勢越明顯�。? 最后��,小芯片能靈活滿足不同功能需求���。? 一方面���,小芯片方案具備良好的可擴展性。例如構(gòu)建了一個基本die后����,可能只用一個die可應(yīng)用于筆記本電腦�����,兩個可應(yīng)用于臺式機�����,四個可應(yīng)用于服務(wù)器��。? ?另一方面����,小芯片可以充當(dāng)異構(gòu)處理器����,將GPU����、安全引擎��、AI加速器、物聯(lián)網(wǎng)控制器等不同處理元素按任意數(shù)量組合在一起�,為各類應(yīng)用需求提供更豐富的加速選擇����。

? 隨著小芯片的優(yōu)勢逐漸顯露�����,它正被微處理器���、SoC、GPU和可編程邏輯設(shè)備(PLD)等更先進和高度集成的半導(dǎo)體設(shè)備采用�。

??根據(jù)研究機構(gòu)Omida統(tǒng)計�����,微處理器是小芯片最大的細分市場���,支持小芯片的微處理器市場份額預(yù)計從2018年的4.52億美元增長到2024年的24億美元。

??同時���,計算領(lǐng)域?qū)⒊蔀樾⌒酒闹饕獞?yīng)用市場�,今年有望占據(jù)小芯片總收入的96%�。

03

六年跋涉,從各自為營到走向標準化??

? 芯片巨頭們對風(fēng)向的變化尤為警覺�,沒有誰想從神壇上跌落����。在守著最先進設(shè)計和制造技術(shù)的同時,他們必須為自己提前探好新的可行之徑�。

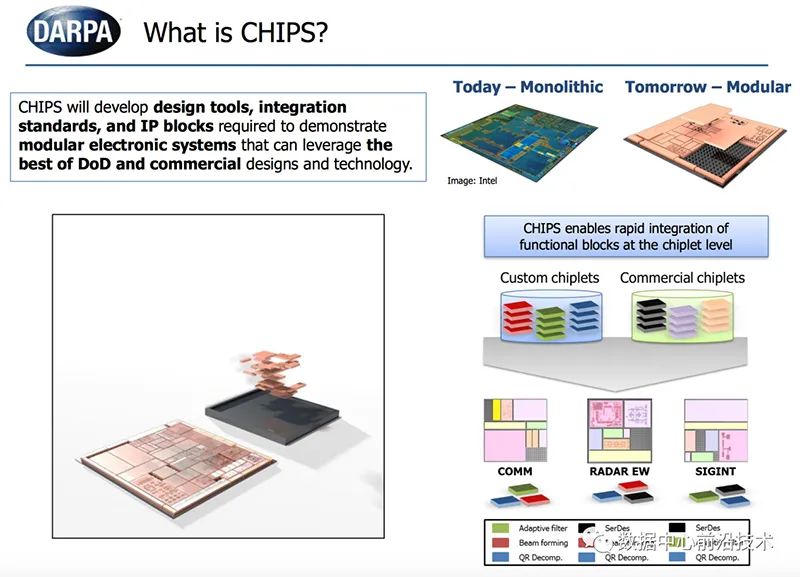

? 也正因為如此��,英特爾、AMD等芯片領(lǐng)軍企業(yè)不僅成為最早的小芯片采用者和倡導(dǎo)者��,也是推動小芯片標準化工作的核心貢獻者��。? 早在2014年,華為海思與臺積電曾合作秀出一款采用臺積電CoWoS技術(shù)的網(wǎng)絡(luò)芯片�����,將16nm 32核Arm Cortex-A57與28nm邏輯和I/O芯片組合在一起,在相同功耗下速度較28nm HPM提升40%����。? 2016年�,Marvell和Kandou Bus宣布一項協(xié)議�,Marvell采用了Kandou Glasswing IP作為芯片到芯片的接口���,將多個芯片相連接。? 美國國防部高級研究計劃局(DAPRA)則在2017年8月啟動“通用異構(gòu)集成及IP復(fù)用策略(CHIPS)”項目��,這是DAPRA總投資15億美元的“電子復(fù)興計劃(ERI)”中的一部分,意在促成一個兼容����、模塊化����、可重復(fù)利用的小芯片生態(tài)系統(tǒng)。?這些小芯片能將各種類型的第三方芯片像堆積木一樣快速混搭成一個系統(tǒng)����,實現(xiàn)數(shù)據(jù)存儲����、信號處理�����、數(shù)據(jù)處理等豐富的功能����,還能將電路板整體尺寸縮小到常規(guī)芯片大小���,從而提高能效����。

? 理想狀態(tài)下,借助小芯片方法��,芯片設(shè)計公司只需專注于自己擅長的IP����,而不必擔(dān)心其余IP���,既有助于提升核心創(chuàng)新能力�,又經(jīng)由多種IP設(shè)計分攤了研發(fā)成本。

? DAPRA向英特爾���、美康�����、Cadence�����、思諾思科技等芯片企業(yè)以及一些大型軍工企業(yè)、高?�?蒲袌F隊伸出橄欖枝��,邀請他們作為項目的主承包方。? 作為CHIPS項目的核心成員之一�,英特爾推出高級接口總線(AIB)�,作為chiplet架構(gòu)的免版稅die-to-die接口標準�。? 例如,英特爾的Stratix 10����、Agilex FPGA均使用相同的AIB接口來集成多種不同的小芯片�。在CHIPS項目的支持下����,許多不同企業(yè)及高校正在用AIB打造小芯片系統(tǒng)����。? 英特爾也是開放計算項目開放特定域架構(gòu) (OCP ODSA)基金會的成員��,該基金會正在促進標準和技術(shù)的發(fā)展����,以幫助實現(xiàn)高級封裝策略。

? 英特爾將其服務(wù)器處理器�����、FPGA����、PC芯片等作為小芯片技術(shù)的商業(yè)試煉場�����,AMD亦將小芯片用在了服務(wù)器和客戶端CPU中���。

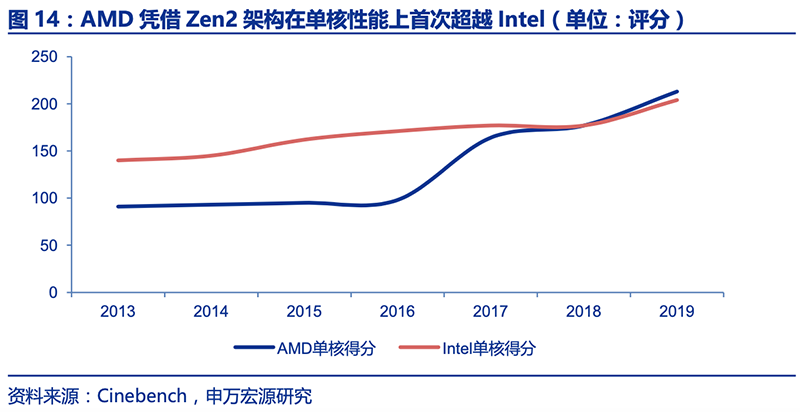

? 2017年����,AMD在其Zen 2架構(gòu)中用小芯片來開發(fā)Epyc服務(wù)器處理器Naples�,隨后又在次年推出的企業(yè)級EPYC處理器Rome中支持8個小芯片�,最多支持64個核心��。

? AMD在2019年推出的Zen 2處理器系列���,單核性能首次超過英特爾�����。

04

粘連小芯片的關(guān)鍵“膠水”

? 具體打造小芯片系統(tǒng)的過程,可就不像搭樂高積木那么簡單了�。

? 如何選擇不同小芯片的設(shè)計方案�����、怎樣實現(xiàn)小芯片間的連接等一系列權(quán)衡均會影響最終的處理速度、功耗和成本�����。? 其中,為了達到接近或媲美單片芯片的性能需求�����,承擔(dān)著“拼接”、“組裝”功能的先進封裝和互連技術(shù)尤為重要�����。? 高帶寬互連技術(shù)則在小芯片之間搭建了一條條“高速公路”�,而2.5D�、3D先進封裝技術(shù)能大幅縮減芯片尺寸�,提供更優(yōu)化的復(fù)雜芯片集成方案���。? 這些技術(shù)的持續(xù)演進����,正為小芯片的興起提供關(guān)鍵的技術(shù)支柱���。

1�、AMD:Infinity Fabric與X3D

? AMD從第一代Zen架構(gòu)處理器開始引入了自研芯片內(nèi)����、外部互連技術(shù)Infinity Fabric(IF)����。

? 該技術(shù)集數(shù)據(jù)傳輸與控制于一體��,由用于傳輸數(shù)據(jù)的Infinity Scalable Data Fabric(SDF)和負責(zé)控制的Infinity Scalable Control Fabric(SCF)兩部分組成。? IF總線可根據(jù)不同SoC優(yōu)化配置��,不僅能實現(xiàn)多個小芯片間的高速互連�,也能實現(xiàn)服務(wù)器中多個CPU插槽間的高速互連�����,第二代IF總線還能提供CPU到GPU的連接,不過CPU到GPU的連接仍然基于PCIe。▲AMD先進封裝技術(shù)進化歷程

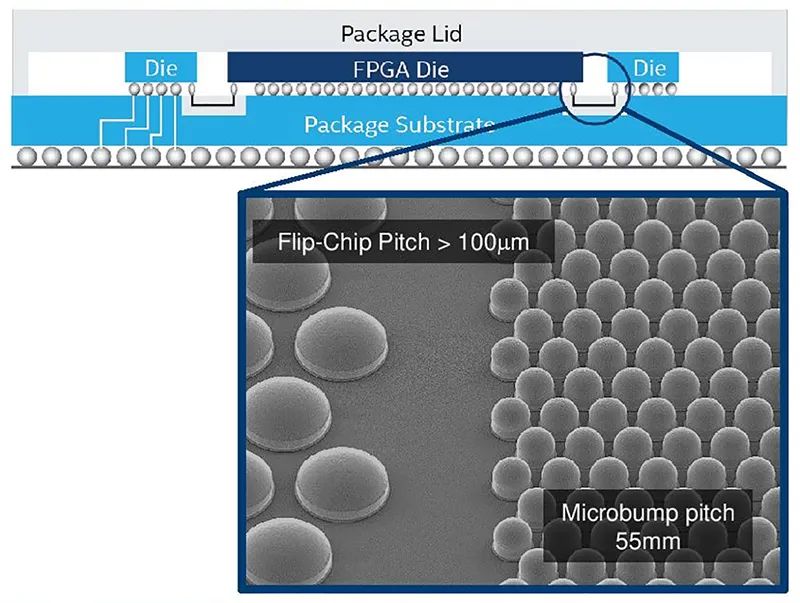

? 在今年的財務(wù)分析師會議上��,AMD透露了將于今年年底發(fā)布的Zen 3架構(gòu)處理器中�,IF總線將升級到第三代���,可實現(xiàn)CPU與GPU之間的內(nèi)存一致性��,通過減少數(shù)據(jù)移動進一步提升性能并減低延遲���。? 下一代IF被稱為Infinity Architecture����,總線帶寬是PCIe 4.0的兩倍����,最多支持8個GPU芯片的連接,而且還支持CPU到GPU的連接���,預(yù)計這將給未來的APU帶來更大的性能提升。? 按照AMD的路徑規(guī)劃,首批Zen 3架構(gòu)處理器將率先用于EPYC服務(wù)器處理器中�����,之后再用于桌面處理器��。? 在此前的Zen架構(gòu)上,AMD已嘗試過多種MCM(Multi-chip module)封裝��。? 據(jù)悉,AMD計劃在未來的產(chǎn)品中引入一種結(jié)合2.5D和3D堆疊的新封裝技術(shù)X3D����,具體詳情尚未透露���,預(yù)計會現(xiàn)身于Zen 4處理器。? 2���、英特爾:EMIB�����、Foveros�、ODI? 英特爾的高級封裝產(chǎn)品包括2.5D EMIB����、3D堆疊Foveros以及兩者組合而成的Co-EMIB��。? 嵌入式多互連橋(EMIB)可以被看作將兩個小芯片連接在一起的高密度橋梁,在二維平面上實現(xiàn)Die-to-die的互連����。? 它是一塊非常薄的硅中介層��,微型凸點密度遠高于標準封裝基板���。使用EMIB����,可以準確在所需位置使用高密度互連�,在其他位置用標準封裝基板互連,這樣就可以節(jié)約一定成本��。

▲英特爾EMIB技術(shù)

? 英特爾當(dāng)前有兩種基于EMIB的解決方案����。? (1)移動PC處理器Kaby Lake-G:用EMIB集成AMD Radeon GPU和HBM���,然后在封裝內(nèi)用PCIe來集成GPU和英特爾CPU,從而實現(xiàn)更緊密地協(xié)作和更小的尺寸�����。? (2)Stratix 10 FPGA:中央FPGA周圍有6個小芯片���,包括4個高速收發(fā)器小芯片和2個高帶寬存儲小芯片��。英特爾在示例中集成了來自3個不同代工廠的6個不同技術(shù)節(jié)點。? 截至今年1月��,英特爾已經(jīng)出貨了200萬個基于EMIB封裝的芯片。隨著該技術(shù)日益普及�,其應(yīng)用范圍將覆蓋至PC����、服務(wù)器�����、5G芯片、GPU顯卡等�����。? 除了EMIB外,英特爾還研發(fā)了3D封裝技術(shù)Foveros�����,通過硅通孔(TSV)�,能像蓋房子一樣將邏輯芯片模塊層層堆疊���,不僅將不同IP模塊有機結(jié)合,還節(jié)省了芯片空間�,并保證功耗不會顯著增加���。

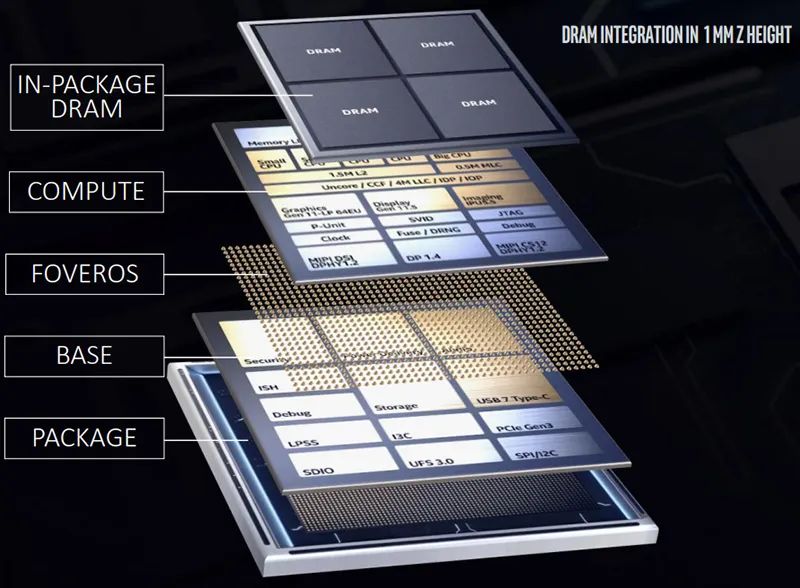

▲Lakefield內(nèi)部架構(gòu)

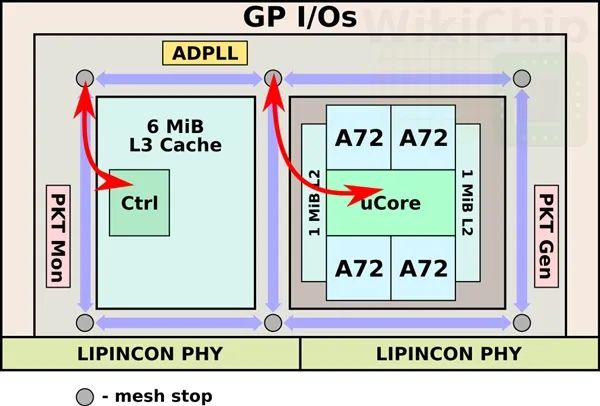

? 去年1月�,英特爾發(fā)布Lakefield移動處理器產(chǎn)品��,它有兩個有意思的技術(shù)要點,一是有具有不同內(nèi)核的big.little混合體系架構(gòu)����,另一個即是小芯片設(shè)計��。? 在Lakefield中�����,計算晶片(Compute die)負責(zé)計算處理,采用最先進的10nm����、7nm、5nm工藝�;基礎(chǔ)晶片(Base die)主要實現(xiàn)I/O功能�����,性能相對不敏感����,可采用22nm等成熟制程工藝����。? 為了適應(yīng)更輕薄的物聯(lián)網(wǎng)���、邊緣計算等場景,英特爾推出的Co-EMIB將EMIB的橫向拼接能力和Foveros的縱向疊加能力相結(jié)合��,通過EMIB連接多個3D Foveros芯片���,制造出比單片芯片更大的靈活可擴展芯片設(shè)計,同時能實現(xiàn)近乎于SoC級高度整合的低功耗�、高帶寬、高性能表現(xiàn)��。? 在此基礎(chǔ)上����,英特爾提出全方位互連(ODI)微縮技術(shù)��,頂部芯片可像EMIB一樣實現(xiàn)小芯片之間的水平通信�����,也可以像Foveros一樣通過硅通孔(TSV)與底層裸片進行垂直通信�����,從而實現(xiàn)以前3D堆疊無法達到的性能����。? 3����、臺積電:LIPINCON�����、CoWoS����、SoIC? 2019年6月����,臺積電在日本舉辦的超大規(guī)模集成電路研討會(VLSI Symposium)期間展示了一顆自研7nm小芯片This���。

? This尺寸為4.4x6.2mm,采用CoWoS晶圓基底封裝和雙芯片結(jié)構(gòu)�,一個芯片內(nèi)建4個Cortex A72核心,另一個內(nèi)建6MiB三緩���。同時,臺積電還開發(fā)了稱之為LIPINCON互連技術(shù)���,信號數(shù)據(jù)速率8GT/s�����。? Chip-on-Wafer-on-Substrate(CoWoS)是臺積電設(shè)計的基于2.5D晶圓級多芯片封裝技術(shù),各芯片通過硅中介層上的微型凸塊結(jié)合在一起��,形成晶圓上芯片(CoW)�,然后將CoW減薄���,露出TSV通孔����。

▲臺積電CoWoS

? CoWoS和InFO均為2.5D封裝技術(shù)����,前者側(cè)重于高端市場�����,連線數(shù)量偏多���,后者針對高性價比市場,連線數(shù)量相對較少�。

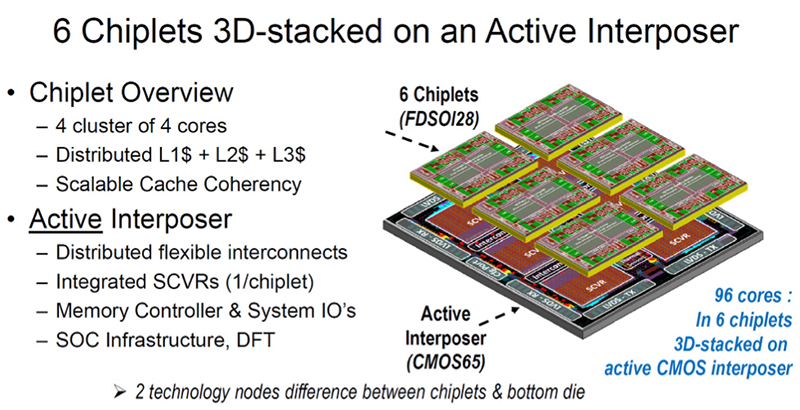

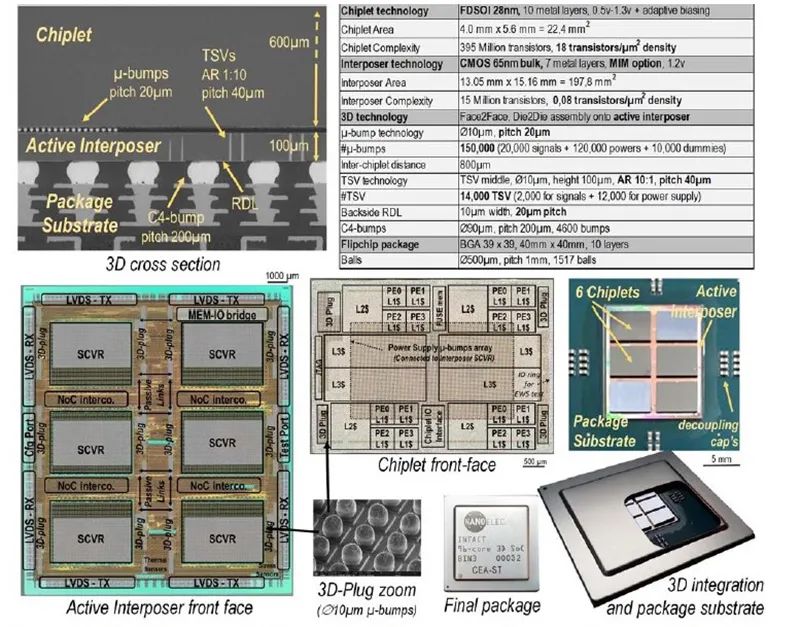

? 基于CoWoS與多晶圓堆疊(WoW���,Wafer on wafer)技術(shù),臺積電研發(fā)了新一代3D封裝技術(shù)SoIC�����,可將不同尺寸���、制程工藝及材料的小芯片組合��。? 相較傳統(tǒng)3D封裝技術(shù),SoIC的凸塊密度和傳輸成本更高���,功耗更低,且能通過與CoWoS或InFO技術(shù)整合其他芯片�����,打造3D x 3D系統(tǒng)級解決方案�����。? 在今年的IEEE固態(tài)電路會議(ISSCC)上����,法國研究機構(gòu)CEA-Letu用6個16核小芯片創(chuàng)造了一個96核處理器���,算力達到220 GOPS,功率為156mW�����。

? 硅中介層和嵌入式硅橋是滿足數(shù)據(jù)速率和延遲需求的關(guān)鍵技術(shù)����。此前常用于小芯片集成的大規(guī)模中介層技術(shù)有2.5D無源中介層��、有機襯底和硅橋等����。

? 這些技術(shù)普遍存在的缺點是不能實現(xiàn)靈活的遠距離小芯片間通信�����,因而難以連接更多小芯片���。它們還難以實現(xiàn)異構(gòu)小芯片的平滑集成和低擴展功能的輕松集成。? 對此����,CEA-Leti引入了有源中介層(active interposer)技術(shù)和3D堆疊技術(shù)來克服這些限制�����,以實現(xiàn)大規(guī)模計算系統(tǒng)的設(shè)計��。? 該芯片將6個采用意法半導(dǎo)體28nm FDSOI制造工藝的小芯片堆疊在一個到200mm2的有源中介層上�,該中介層將直通硅通孔(TSV)嵌入到65nm技術(shù)節(jié)點��。

▲CEA-Leti芯片顯微照片�、3D截面����、封裝和技術(shù)功能

? 每個小芯片包含16個MIPS32v1核心�,有源中介層集成了開關(guān)電容器穩(wěn)壓電路、靈活的分布式互聯(lián)和將內(nèi)核的片上存儲器各個部分連接在一起的網(wǎng)絡(luò)�����,可提供節(jié)能的多核計算架構(gòu)�。? 整個系統(tǒng)架構(gòu)在所有小芯片計算區(qū)塊之間提供了完全可擴展的分布式緩存一致性架構(gòu)����,這些架構(gòu)通過活動中介層互連�����。該架構(gòu)允許通過緩存層次結(jié)構(gòu)輕松部署軟件��,從而實現(xiàn)高達512核的完整系統(tǒng)可擴展性�。? CEA-Leti的科學(xué)總監(jiān)Pascal Vivet認為��,不同供應(yīng)商的小芯片接口未必兼容���,需要一種能將它們粘合在一起的新方法�����,而有源中介層是小芯片技術(shù)的最佳選擇。?05

結(jié)語:通向下一節(jié)點的低成本路徑

? 小芯片并非完美的,如今在小芯片探索的道路上��,流量擁堵���、散熱、電源管理��、測試等問題均是系統(tǒng)架構(gòu)設(shè)計仍待克服的主要挑戰(zhàn)���。? 盡管有DAPRA CHIPS��、OCP ODSA等項目在著力推進小芯片接口標準化����,但獨立第三方小芯片供應(yīng)的商業(yè)模式何時能在芯片產(chǎn)業(yè)中普及�,當(dāng)前尚未可知���。? 也許任何一種方法很難“單槍匹馬”就挽救摩爾定律�����,但不可否認的是���,小芯片這種新興方法正在改變芯片的設(shè)計和集成策略��,以更靈活的混合搭配系統(tǒng)方案,為芯片公司提供了遷移到下一個節(jié)點的低成本路徑����。? 處于這樣一場新革命的開端,無疑是一件激動人心的事�。